## (China)

Accelerate the realization of heterogeneous integration technology in the semiconductor industry, and introduce new technologies and capabilities – September 13, 2021

## 加速半导体产业实现异质集成技术,应材公司推出新技术与能力

2021-09-13 18:14 十轮网

近期,半导体异质集成技术容许不同技术、功能和尺寸的芯片集成在一个封装中,为半导体和系统公司带来了新的设计和制造的灵活性。美商应用材料公司将其在制程技术和大面积基板方面的领导地位与生态系统统的合作结合起来,以加速产业的异质设计和集成发展。

应材指出,异质集成让不同技术、功能与尺寸规格的芯片得以集成在一个封装中,让半导体与系统企业获得前所未有的设计与制造弹性。应用材料公司结合其领先业界的先进封装与大面积基板技术,与产业合作伙伴携手开发新解决方案,大幅改善芯片功率、性能、单位面积成本与上市时间 (PPACt)。而针对异质集成先进封装技术,应用材料公司发布了3项至关重要的创新,包括裸晶对芯片混合键合、芯片对芯片叠合与先进基板。

首先,加速裸晶对芯片的混合键合 (Die-to-Wafer Hybrid Bonding) 技术。应材表示,裸晶对芯片混合键合使用铜对铜直接互联技术,提高I/O密度并缩短小芯片之间的线路长度,进而提升整体性能、功率与成本效益。为加速此技术的开发,应用材料公司在其先进封装研发中心添加了先进软件模拟功能,在进入硬件开

发阶段前先行评估与优化各种参数,例如材料选择与封装架构,协助客户缩短学习周期与产品上市时间。 这些是应用材料公司与贝思半导体 (BE Semiconductor Industries N.V., Besi) 在2020年10月发布的共同开 发协议中提到的功能。此协议的目的是率先为裸晶型混合键合技术,提供完整且获产业认可的设备解决方 案。

其次,为芯片对芯片混合键合开发协同优化的解决方案 (Wafer-to-Wafer Hybrid Bonding)。是芯片对芯片接合技术,能让芯片制造商在单一芯片上设计特定芯片架构,并在另一片芯片上设计不同的架构,再借由这两片芯片的接合,制造出完整的设备。为了达到高性能与良率,前段制程步骤的品质非常重要,接合时的均匀度和对准度也不容忽视。因此,应用材料公司同时也宣布与益高科技 (EVG) 签订联合开发协议,共同为芯片对芯片接合开发协同优化的解决方案。这项合作将结合应用材料公司在沉积、平坦化、植入、测量与检验领域的专业能力,以及EVG在芯片接合、芯片前置处理与活化,以及接合对准和叠对测量方面的顶尖技术。

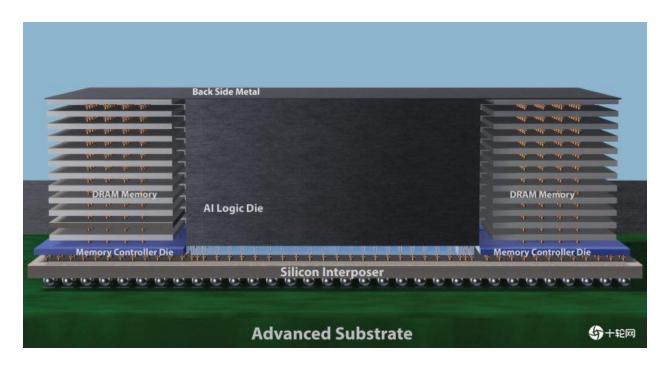

最后,在利用更大面积、更先进的基板以获得PPAC优势上,由于芯片制造商不断在精密的2.5D与3D封装设计中植入更多芯片,使得更先进基板的需求与日俱增。应用材料公司也运用最近收购的Tango Systems提供的先进面板制程技术,来增加封装尺寸与互联密度。相较于芯片尺寸的基板,500 mm²以上的面板尺寸基板能够封装更多芯片,进而提升芯片的成本效益、功率与性能。而随着客户开始采用这些较大面板尺寸的基板,应用材料公司也通过旗下的显示器业务群提供大面积的材料工程技术,包括沉积、电子束测试(eBeam testing; EBT)、扫描式电子显微镜 (SEM) 检测与测量,以及针对缺陷分析的聚焦离子束 (FIB)。

应用材料公司先进封装企业副总裁Nirmalya Maity表示,应用材料公司拥有业界首屈一指的先进封装解决方案产品组合,能为客户提供最广泛的异质集成技术选择,通过与业界其他公司的合作,协同优化产品技术,并创建新的生态系统统,帮助客户加速达到PPACt的目标,为应用材料公司开创新的商机。

(首图来源:应用材料)

https://www.toutiao.com/i7007356327823704613/?wid=1634924107484