## Emerging Metrology Requirements for Heterogeneous Integration and 3D Packaging – July 7, 2021

## 異質整合/3D封裝崛起

# 量測新需求應運而生

Thomas Uhrmann

定套傳統2D製程微縮能創造的成本 更效益越來越低,半導體業開始轉 戰3D整合與異質整合。異質整合是將製 造、組裝與封裝等多種不同的元件或具備 不同特徵尺寸與材質的電晶體,整合進單 一裝置或封裝裡,以提升全新一代裝置的 效能。

要實現3D整合或異質封裝,晶粒到晶 圖(D2W)固然是非常重要的製程步驟,但 量測亦扮演十分重要的角色。本文將檢視 量測在各個關鍵製程步驟的重要性,以及 量測對異質整合元件生產良率的提升,能 帶來哪些助益。

由於3D封裝(3D-IC、3D系統單晶片等) 的互連問距隨著每個新的生產世代越來越 為緊密,晶團與晶粒接合對準與層疊的製 程也需跟著一起微縮,並需具備更高精準 度與更頻繁的測量,讓發生製程問題時可 以找出原因,以便提供矯正動作或是重新 作業的可能性,最終才能帶來更高的生產 良率。

另一方面,扇出型晶圖級封裝 (FOWLP)若採取晶片先裝/面朝下(chipfirst/face-down)的組態,會使用暫時性 接合的載具。如此一來,在壓膜或基板 剝離過程中產生的封膠翹曲與收縮,會 帶來晶粒的位置移位與旋轉等挑戰。由 於導線互連與線寬/線距(L/S)的密度正 在增加,因此高精度測量晶粒位置相當 重要。無光單微影透過使用自適應圖案 (Adaptive Patterning)技術,提供一個有 效且多功能的晶粒移位解決方案,原因 是它可以個別地為每個晶粒、系統與晶 圖錯位的線路圖型進行補價。不過,這 也帶動需要晶粒位置與晶圖形狀關鍵資 訊的量測需求。

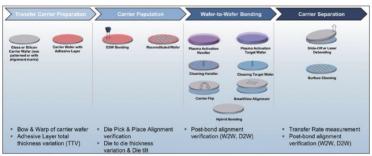

整體來說,這些不同的異質整合製程步 驟擁有獨特的一套量測需求(圖1),我們 可以透過EVG 40 NT系列的自動化量測系 統,達成這些需求。

#### 整合間距推動全新的量測需求

我們之所以能促成系統整合,主要是 依靠不同類形的封裝,在這些封裝過程 中,具備不同功能的晶粒,藉由如銲線 接合(wire bonding)與錫鉛凸塊等標準 的互連技術完成連接。對於這些3D系統 級封裝(3D SiP)裝置來說,導線間距縮 短至30微米是很正常的,對於矽中介層 (Interposers)與如堆疊式的記憶體立方

圖1 3D與異質整合領域即將到來的新興量測需求

圖2 晶圖對晶圖對照圖顯示接合的不同組成

體等3D堆疊式IC, 銲錫微凸塊(Solder micro-bump)的導線間距正微縮至10微米 或是更低。10微米間距已成為導線互連 技術的一個匯合點。另一方面,它也被視 為混合式接合的反曲點。同時,這些極為 緊密的間距也讓裝置得以使用晶粒到晶圓 (D2W)混合式接合或晶圓到晶圓(W2W) 混合式接合技術,依功能性劃分至不同的 小晶粒(Chiplet)。

#### 晶圓到晶圓接合的量測需求

W2W接合製程促成全新的裝置製造概 念,例如將NAND、DRAM、SRAM或 Flash等記憶體層從一個晶圓轉移到另一 個晶圓達成的記憶體存取邏輯裝置,以 及背照式影像感測器與其它異質整合的 裝置應用。在W2W接合過程中改善晶圓

間的疊層,可以讓不同層在早期的金屬 階段完成連結,不僅可以節省成本,同 時提升裝置的頻寬與效能。對於約十年 前生產第一代影像感測器,500奈米到1 微米範圍的W2W疊層已經足夠。隨著好 幾世代的裝置發展,此一範圍已快速縮 小。如今,許多的應用與不同的整合應 用,讓所需求的範圍已達到4微米的導線 間距,到研究用的500奈米導線間距。因 此,如今先進應用的W2W疊層需求,使 疊層間距範圍下探至500奈米到100奈米 不等。

圖2針對總疊層誤差中不同的誤差組成 提供總覽。透過高精度量測,比較兩個晶 圓的基準點,將其分為個別的誤差條件。 透過紅外線來透視矽晶圓,可以測量面對 面接合的晶圓堆疊中兩個晶圓的所有基準

更緊密的互連間距,同時帶動對更高晶 圓接合與量測效能的需求。1微米以下的 間距,對位的準確度需要達到50奈米, 並意味著測量設備的精準度必須達到10 奈米以下。EVG GEMINI FB XT融合式 晶圓接合平台可以符合這個需求。

我們必須在多處對完成接合的堆疊進行 測量,如此一來不但可以取得單點的疊層 量測值,同時還可產出晶圓堆疊的整體疊 層對照圖,而這張圖可以提供影響良率的 各種製程因素的有用資訊。這些因素包括 接合波速、傳播波形,以及來自兩張接合 晶圓的表面準備情況。

EVG40 NT可以產出這種疊層模型,模 型可以用於回饋迴路提升整體的對準情 況。透過此方式,用戶可以預測製程穩定 的問題,並採取矯正行動來提升良率。

#### 技術紮馬步

圖3 不同整合程度下的集體晶粒到晶團接合的量測需求

#### 晶粒到晶圓接合的量測需求

如先前文章所述,我們可以實作不同的 晶粒到晶圓接合方案,也就是直接配置晶 粒到晶圖(DP-D2W)或是集體晶粒到晶圓 (CoD2W)接合。Co-D2W接合程序的製 造流程如圖3所顯示,並包含四個區塊: 載具準備、載具布植(Population)、晶圓 接合(暫時與永久)以及載具分離。這四個 區塊中的每個環節,都有不同的量測需

針對轉移載具晶圓,使用液態旋塗式 層主要是為晶粒提供一個平坦的基礎。 暫時性接合膠層厚度與均匀度,在這個 階段極為關鍵。下一個步驟是載具上晶 片佈植、通常晶粒與載具都有對準的對 準基準點,它們的功能就是在達成完整 布植後,圖案與對準驗證的基準。為了 檢查是否出現對準誤差,我們通常會使 用兩個看得到的記號的比較量測值,來 檢查放置的準確度。

由於混合式接合未來將鎖定互連問距約 介於10微米與2微米之間,配置的準確度 與量測也必須進行同樣的微縮,以便控制 與產出製程。一般來說,10微米的問距 可以轉化成1微米的晶粒對準與約為1微 米的測量精準度, 這點目前已經可以做

若未來發展路徑鎖定2微米的互連問距 時,配置準確度與量測精準度必需提升 十倍(各為20奈米)。由於更小的晶粒尺寸 會導致更多的旋轉誤差, 而取放方式卻沒 有變化,這會為低測量精準度帶來更高的 不確定性,使得量測精準度更具挑戰性。 除了這些同一平面的需求外,接合前與接 合後的晶粒與晶圓基準,並不一定會在同 一個平面上,也因此在測量時必須重新對 焦,或採取替代的量測策略。

例如,在堆疊8至16個晶粒層的高頻 寬記憶體(HBM)堆疊情況下,每增加一 層,基底晶圓與每個個別晶粒上的基準對 焦平面就會越發偏移,最多會超過500微 米,與疊層的誤差則是相同的。EVG40 NT系列中的單一一套系統,就能支援所 有來自CoD2W與DP-D2W的量測需求, 且精準度符合當今以及未來晶粒配置量測 的需求。

圖4 EVG LITHOSCALE主動晶粒偏移補償,獲得EVG40 NT晶粒偏移對照 圖的支援

#### 無光罩微影技術的量測需求

如同先前的說明, 晶粒偏移與晶粒旋轉 對於使用環氧樹脂封膠的基板來說,是 FOWLP常見的問題。依據矽晶圓內容、 晶粒分布、封膠材質特性以及封膠前晶粒 取放準確性的不同, 封膠收縮可能讓晶粒 從原本設定的位置跑掉。

對於當前的扇出形封裝,我們可以藉由 額外增加電路層為晶粒錯位的情況提供補 僧,讓標準的步進且重複微影技術可以曝 光,並匹配晶圓上的走線。然而對於中等 圖案密度與較大L/S深寬比的情況而言雖 然可行,若鎖定高效能與高頻寬應用的較 新型產品同時晶粒尺寸必須大於步進且重 複微影技術需要的光環或光罩則需要小於 2微米的L/S深寬例。因此,增加可以緩衝 數微米晶粒偏移的補償層不再那麼簡單可 行,從光罩本身進行補償則成為更有效的 選用方式。

由於這些封膠基板獨特的晶粒錯位圖 形,我們需要準確的額外的晶粒取放與晶 粒偏移量測。擷取到的取放座標數據,不 是用來主動補償總體失真模型,就是用來 打造自行調適的微影光罩。失真補償演算 法包括對旋轉、微縮、剪切與平移(偏移) 的數學矯正。

針對晶粒取放誤差的補償,每個晶粒取 放都會利用每顆晶粒上的兩個點進行記 錄,成為整體晶圓上該位置的一個函數。 有鑑於轉換過程的即時性,個別從外部取 得的晶粒量測數據產生動態二進位圖案剛 好在曝光前配合每個基板,來補償處置或 預處理造成的疊層/定位誤差,但排除潛 在的熱影響。圖4透過圖像化顯示晶粒層 級補償的簡化流程。

#### 可擴充至大批量製造

在上述特別說明的應用當今量測設備已 經使用當中。不過,由於先進的封裝發 展藍圖驅動市場對更精密的對準、取放 與補償規格的需求,量測解決方案必須 同時提供更高的資料密度與準確性,這 也意謂對於3D與異質整合的新興量測, 測量精準度與產出是最重要的兩項規

(本文作者為EVG事業開發總監)

### 參考資料

[1] E. Beyne, Semi 3D Summit 2019