# (Taiwan)

## Interconnect Density Quest for Endless Melt/Hybrid Bonding is Key - April 16, 2022

图2 混合报台的物理模则构虑理流程,虑理步频與电流活化溶散报合相同,但调整从要與介电信平行虑理

誘流台接合因為維姆將問距縮小到10個米以下,提供更大的互達密度與通訊擴高。因此能取代傳統使用銅製數凸線 (Microbump),作為中庭和高階對韓的互達方案,混合接合的主要應用包括互補式金屬氧化物半導體(CMOS)影像原測器。 3D地區的NAND與DRAM配傳程,以及3D系的單寫片(SoC),如表1所示。

|                      | Backside                         | Memory                                        |                                              | Logic             |                 |

|----------------------|----------------------------------|-----------------------------------------------|----------------------------------------------|-------------------|-----------------|

| Device +             | Illuminated<br>image<br>Sensor   | 3D NAND<br>Flash<br>NAND Block<br>* Periphery | Next Gen.<br>Memory<br>Memory +<br>Periphery | SoC Partitioning  |                 |

|                      | Photo Diode<br>+ DRAM +<br>Logic |                                               |                                              | SelC              | SRAM +<br>Logic |

| Bonding<br>Process   | W2W                              | W2W                                           | W2W                                          | W2W and/or<br>D2W | W2W             |

|                      | hybrid                           | hybrid                                        | fusion 8.<br>hybrid                          | hybrid            | hybrid          |

| Pitch                | 2µm → 1µm                        | 2µm → 1µm                                     | 2µm →<br><1µm                                | Эµпе → 2µпе       | 2µт             |

| Post Bond<br>Overlay | <100nm                           | <150nm                                        | <100nm                                       | <200nm            | <200nm          |

#### 混合接合更緊密的需求

日益增加的頻度需求,显促使半導體與界離級異質醫者的主因之一。而頻度要增加,互應的關語線小,密度揭高,显如新的 指數:互應之間的關語級小。裝置上同樣的百傷可以應成更多的環接,而確也會味養更多的資利能夠結構結。

如国3所示,更高的與賽需求帶動具備更製它關距需求的新型封轄技術。後2.5D經遭到3DIC對裝,以及後3D地產品片 (Stacked IC, SIC)經遭到3D SOC對談。可以為賴寬帶來大幅度的提升。這些嶄新的對談技術需要更繁密的關距。相對的也 會審對對不同接受性能的需定。

图3 朱东的横套黄龙阳斯美国整合四基片准备技術

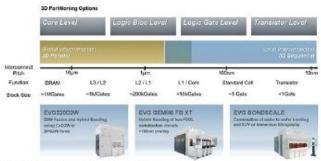

另一個觀察不同異異接合技術在何處應用的方式是特它們與不同的裝置設計和異片分割等項進行比較(图4)。同樣地,隨著 核心能到機關單元與複雜聲,最後到電晶標單,互連闡距裝得更緊要。所需的接合技術也不同。

国4 不同的30分割巡貨等數不同的品周接合需求與技術

## 下朝白皮書

- · 《重導白皮書》歡迎下載!ECAD-MCAD 協同設計達成首次設計即成功的目標

- ・【精雅自安徽】立即下载!Embedded Analytics一種平倫方法

- 【全新白色書】立即下載!在系統單晶月般 計中利用硬體模擬推行功耗分析

- · 【全部白皮書】歡迎下載!喜效船電源模组 封裝的特性

- ·快收職!後疫時代製造業獨型秘笈(整要点 整化學養研攻略)·火熱上聚

在温度到温度的接合中,需要紧密的對導與晶度間處層的構度。以接接合晶度上互達裝置關為良好的電接線。同時終接合介 図的互建回機能至最小,使晶直可以構出更多空間生產裝置。隨着市場對元件I/O性能的短求不虧提升,每一代新產品對晶 圖到最高的複合密度要求,也結果發高。

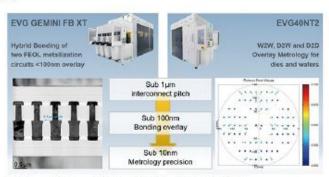

這條年末,島層的技術能力已經顯著提升,代表德密度30晶片堆島的實現與最終的商業化。已提出重大的一步。2017年 時,比利時做電子研究中心(mec)與EVG 利用EVG GEMINI FB XT整合熔融組合系統,將處置到處圍繞合的島層積度縮小 到180余米,成為混合接合技術發展的一個重要里程序。具有可量差的最層積度已經理到100余米,低於75余米的技術則已 在開發中(魯5)。

第5 目前EVG所提供的系统,已经可以在300毫米晶面上,建成纸妆75英米的晶谱模象

区数面的光學對準是處置接合系統效能的開闢,而EVG在20多年數即是開創此技術的先驅。如今,我們利用整合在GEMINI FB XT基面地合素統成的的SmartVew NT3新建模詞,在EVG的最直地合稱上陸低度對面的光學對應。

提合接合的品質到品質數學技術的媒子為當今各種大量應用帶來電腦改差,包括影像緊急器整合的NAND Flash地區,就時 解或CMOS影像歐洲器(BSI CIS)而言,高磷度的品質到品質到達可以養現讓取經度更快,支援全域快門功能的影像歐別 器。全域快門在汽車應用中特別指幫的,因為讓取經度不夠快的影像歐別器,提到高速認動的物件,很容易排取到模糊的影像。 像。全域快門功能就是接個問題的経営。

混合接合同時能在影像家劍器中加入更多的運算功能,針對如人體蚌麇等安全性應用來說相當有幫助,對於NAND Flash達 異,認合接合可以用來結合分開處理的CMOS與配德體晶團、透過此方式,提倡電節位於配德體上能帶來更高的位元空度。

陽審記榜聽審的數量從日前主法的128層釋加到196層,記憶雜暴粒的姿度也隨之擇加・四此,互繼密度也以類似的規模境 加,並推動最間到最固定自中前異層的亲求。

### 封準/疊層精度模有突破 異質整合之路更好走

随著傳統的2D矽磊團指充受成本上的時間,半導程臺灣轉而設力於包括3D是片塔島的異菌融合,以便提升裝置的效能,基 圖到異圖接合是實現3D/異質整合的腦證報程,同時需要緊密的對連與異音構度,使互連裝置閩南原好的電換體,

随着互建物现在每一代标音品推出准数末越聚在,品面影響與黑層其程也須以更古的資金進行相應的模文。品面到品面接合 技術的研發展,包括搭載Smarfview NT3對準備紹的GEMINI FB XT整合式溶粉接合系统,可以為配得程准置。3D系統編集 片(SoC)、范萨式CMOS影像原列器堆差與基础分割等應用等來對準與基準穩度的提升。

(本文作者為EVG事業開發總監)