Interconnect Density Quest for Endless Melt/Hybrid Bonding is Key – April 1, 2022

設備與材料 技術解密

Thomas Uhrmann

在 半導體製造中,3D 垂直堆疊與異 質整合(將多種不同元件與品粒製 造、組裝與封裝成單一裝置或封裝),對 半導體元件的功耗、效能、面積與成本 (PPAC)的最佳化,是十分重要的手段。

在本系列的前三篇文章中,我們回顧了 數種促成異質整合進展的革命性全新製程 技術,包括晶粒到晶圖(D2W)接合與無光 單微影。本文將探討一種針對3D/異質整 合的新技術,也就是晶圓到晶圓(W2W) 的熔雕與混合接合,此技術目前還在初期 發展階段,但在過去幾年來有相當快速的 進展,讀品片製造商能夠持續擴展其先進 封裝產品路線圖。

## 熔融與混合接合應用逐步擴展

增職接合或直接品圖接合,是在兩個彼 此接觸的平滑表面上,利用原子化學接合 產生的附著力,來進行接合的技術,熔融 接合在氫橋鍵的協助下,可以讓介電層(又 稱活化羥基官能基)在品圓間進行接合。

這道製程包含兩個步驟,一是品圖在室 溫下接觸,又稱預接合;二則是在攝氏 900~1,200度溫度範圍內進行熱退火,以 便在品圓間建立共價鍵,由於退火過程的 高溫, 品國間的氧化物介面會變得點稠, 填滿兩片品圖接觸面的所有間隙, 進而產 生連續且無任何空隙的接合介面。

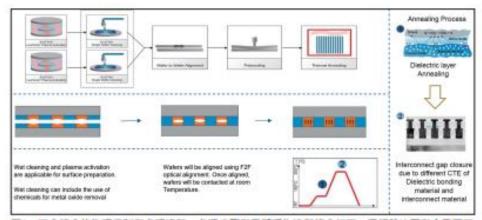

利用熔雕接合進行主動裝置整合的一項 突破,就是電漿活化熔雕接合(圖1)。在該 製程中,基板表面在接合前會塗上一層電 漿。受電漿處理的表面將發生變化,產生 更高的能量接合,並縮短最終熱退火步驛 的處理時間,且溫度也較低(攝氏250~350 度)。接著會施以清洗,以進一步進行表面 處理並最佳化接合強度。兩片晶圓隨後會 利用面對面的光學對準技術進行對準,

對準後,兩片品圖會放置在一般的無塵 室,並在室溫環境下彼此接觸,即預接 合。在最後的熱退火過程中,低能量的氫 橋鍵會轉化成共質鍵,並在晶圓間形成永 久的連結。

增融接合最初是應用在絕緣層上覆砂 (Silicon on Insulator, SOI)品圓等工程基 板的製程技術,但現在已演進成利用全範 圖的介電質熔融接合來堆疊品圓的技術。

銅墊片可以與介電層平行處理,使其在 室溫下對介電層進行預接合,並在退火 過程中透過金屬擴散接合達成電接觸(圖 2)。這種情況稱為混合接合。

2 混合接合的物理機制與處理流程。處理步驟與電源活化熔融接合相同,但鋼墊片要與介電層平行處理

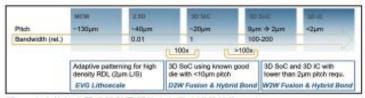

銷混合接合因為能夠將問距縮小到10 微米以下,提供更大的互連密度與通訊 頻寬,因此能取代傳統使用銅製微凸塊 (Microbump),作為中階和高階封裝的互 連方案,混合接合的主要應用包括互補式 金屬氧化物半導體(CMOS)影像感測器、 3D堆疊的NAND與DRAM記憶體,以及 3D系統單晶片(SoC),如表1所示。

## 混合接合更緊密的需求

日益增加的頻寬需求,是促使半導體業 界擁抱異質整合的主因之一,而頻寬要增 加,互連的問距縮小,密度提高,是必然 的趨勢,互連之間的問距越小,裝置上同 樣的面積可以達成更多的連接,而這也意 味著更多的資料能夠被傳送。

如圖3所示,更高的頻寬需求帶動具 備更緊密問距需求的新型封裝技術。從 2.5D過渡到3DIC封裝,以及從3D堆疊 晶片(Stacked IC, SIC)過渡到3D SoC封 裝,可以為頻寬帶來大幅度的提升。這 些嶄新的封裝技術需要更緊密的問題, 相對的也會帶動對不同接合技術的需 求。

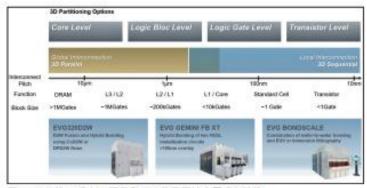

另一個觀察不同晶圓接合技術在何處應 用的方式是將它們與不同的裝置設計和品 片分崩還項進行比較(圓4)。同樣地、隨 著核心級到邏輯單元與邏輯開、最後到電 晶體層,互連問距變得更緊密,所需的接 合技術也不同。 在晶圓到晶圓的接合中,需要緊密的對 準與晶圓間疊層的精度,以讓接合晶圓上 互連裝置間有良好的電接觸,同時將接合 介面的互連面積降至最小,使晶圓可以騰 出更多空間生產裝置,隨著市場對元件I/ O性能的追求不斷提升,每一代新產品對

|                      | Backside<br>Illuminated<br>Image<br>Sensor<br>Photo Diode<br>+ DRAM +<br>Logic | Memory                                        |                                              | Logic             |                 |

|----------------------|--------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|-------------------|-----------------|

| Device<br>Stack      |                                                                                | 3D NAND<br>Flash<br>NAND Block<br>+ Periphery | Next Gen.<br>Memory<br>Memory +<br>Periphery | SoC Partitioning  |                 |

|                      |                                                                                |                                               |                                              | SolC              | SRAM +<br>Logic |

| Bonding<br>Process   | W2W                                                                            | W2W                                           | W2W                                          | W2W and/or<br>D2W | W2W             |

|                      | hybrid                                                                         | hybrid                                        | fusion &<br>hybrid                           | hybrid            | hybrid          |

| Pitch                | 2µm → 1µm                                                                      | 2µm → 1µm                                     | 2µm →<br><1µm                                | 9µm → 2µm         | 2µm             |

| Post Bond<br>Overlay | <100nm                                                                         | <150nm                                        | <100nm                                       | <200nm            | <200nm          |

圖4 不同的3D分割還導帶動不同的晶圓接合需求與技術

品圓到晶圓的接合密度要求,也越來越高,

這幾年來,疊層的技術能力已經顯著提 升,代表高密度3D品片堆疊的實現與最 終的商業化,已邁出重大的一步。2017年 時,比利時微電子研究中心(imec)與EVG

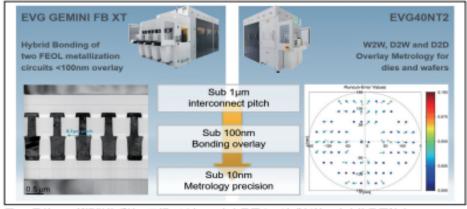

> 利用EVG GEMINI FB XT整合熔融接 合系統,將晶圓到晶圓接合的疊層精 度縮小到180奈米,成為混合接合技 衛發展的一個重要里程碑。目前可量 產的疊層精度已經達到100奈米,低 於75奈米的技術則已在開發中(圓5)。

> 面對面的光學對準是晶圓接合系 統效能的關鍵,而EVG在20多年前 即是開創此技術的先驅。如今,我 們利用整合在GEMINI FB XT晶圆 接合系統內的SmartView NT3對準 模組,在EVG的晶圓接合機上達成 面對面的光學對準。

> 混合接合的晶圓到晶圓對準技術 的進步為當今各種大量應用帶來實 際效益,包括影像感測器整合與 NAND Flash堆疊。就背照式CMOS 影像感測器(BSI CIS)而言,高精 度的晶圓到晶圓對準可以實現讀取 速度更快,支援全域快門功能的影 像感測器,全域快門在汽車應用中 特別有幫助,因為讀取速度不夠快 的影像感測器,遇到高速移動的物 件,很容易摑取到模糊的影像。全 域快門功能就是這個問題的解答。

> 混合接合同時能在影像感測器中加 入更多的運算功能,針對如人臉辨識 等安全性應用來說相當有幫助,對於 NAND Flash堆疊,混合接合可以用來

結合分開處理的CMOS與記憶體品圖。透過 此方式,週邊電路位於記憶體上能帶來更高 的位元密度。

隨著記憶體層的數量從目前主流的128 層增加到196層,記憶體晶粒的密度也隨 之增加,因此,互連密度也以類似的規模 增加,並推動晶圓到晶圓接合中對疊層的 需求。

## 對準/疊層精度屢有突破 異質整合之路更好走

隨著傳統的2D矽晶圓擴充受成本上的 限制,半導體產業轉而致力於包括3D晶 片堆疊的異質整合,以便提升裝置的效 能。晶圓到晶圓接合是實現3D/異質整合 的關鍵製程,同時需要緊密的對準與疊層 精度,使互連裝置問有良好的電接觸。

隨著互連問距在每一代新產品推出後越 來越緊密,品圓對準與疊層製程也須以更 高的精度進行相應的擴充,品圓到晶圓 接合技術的新發展,包括搭載SmartView NT3對準模組的GEMINI FB XT整合式熔 融接合系統,可以為記憶體堆疊、3D系 統單晶片(SoC)、背照式CMOS影像感測 器堆疊與晶粒分割等應用帶來對準與疊層 精度的提升。

(本文作者為EVG事業開發總監)

參考資料

- Semiconductor Engineering, "Bumps Vs.Hybrid Bonding for Advanced Packaging", June 23, 2021, https:// semiengineering.com/bumps-vs-hybridbonding-for-advanced-packaging/

- [2] IEEE Electronics Packaging Society, Silicon Valley Area Chapter, "Bonding Technology for the Next Generation Integration Schemes", June 10, 2021, https: ://ewh.ieee.org/soc/cpmt/presentations /eps2106b.pdf

- [3] ASM International, "Imec and EV Group achieve 1.8µm accuracy in pitch overlay for wafer bonding", https://www.asminternational .org/web/fas/newswire/-/journal\_content /56/10180/27105592/NEWS

- [4] Semiconductor Engineering, "3D NAND's Vertical Scaling Race", December17, 2020, https://semiengineering.com/3d-nandsvertical-scaling-race/