## Micro-Electronics Magazine (Taiwan)

Die-to-Wafer Bonding Steps into the Spotlight on a Heterogeneous Integration Stage - April 6, 2021

### 異質整合重要件日增

# 晶粒到晶圓接合備受矚目

Thomas Uhrmann

學體業目前正遭逢有史以來最劇烈 ★ 的變革。許多新的應用如人工智慧 (AI)、擴增/虛擬實境與自動駕駛需要龐 大的運算力,而處理器則針對每個特定的 應用進行優化。與此同時,開發週期也越 來越短,新晶片的設計、製造成本則呈指 數增長,而且在許多情況下,良率是下降 的。唯有改變整個半導體製程原則,我們 才能解決這些問題。

儘管2D電晶體微縮仍然相當重要,但 與微縮相關的成本及複雜性不斷上升, 已驅使半導體業轉向3D整合與異質整 合,以提升元件性能,滿足上述全新應 用的需求。異質整合是將製造、組裝與 封裝等多種不同的元件或具備不同特徵 尺寸與材質的電晶體,整合進單一裝置 或封裝裡。先進封裝已成為創新首要的 驅動力,它從單片系統過渡到晶粒層級 系統開始,例如最新發表的智慧型手機 的應用處理器,其結合使用先進封裝技 術的處理器、記憶體與AI/神經網路元件 等個別元件。隨著這些元件從晶粒到小 晶片的進一步微型化,此一轉型將在未 來幾年內加速,進而促成客戶與應用需 求間更精準與個別化的對映。

#### Chiplet帶動混合接合需求

把面積數百平方毫米的大型晶片切割成 較小晶片,也就是Chiplet的設計方式,可 以帶來更高的良率並節省成本。此外,只 有需要最新節點微影製程的Chiplet,才 需要使用這類技術進行生產;至於剩下的 Chiplet則可使用較舊世代,成本也較低的 微影製程製造。由於半導體製造的複雜性 與創新越來越朝向先進封裝轉移,使得具 彈性的混合接合技術越來越重要。

透過堆疊與透過電性導通,把來自不 同產品線的晶圓連結起來的晶圓到晶圓 (W2W)混合接合技術,是異質整合的 核心流程,它對於互補式金氧半導體

| 表1       | 可供異質整合使用的混合晶粒到晶圓接合法                                                |                                                                                          |

|----------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|          | Co-D2W                                                             | DP-D2W                                                                                   |

| 轉移<br>方法 | 藉由重新建構載具進行的集體晶粒轉移                                                  | 使用覆晶黏晶機進行活化晶粒的直接<br>替换                                                                   |

| 優點       | 已被驗證的技術     届粒活化與清洗相當於W2W<br>混合接合     氧化物管理     載具重做具可行性           | 多用途的方法     最粒厚度不變                                                                        |

| 缺點       | 較差的對準精度,由於D2W + W2W<br>誤差的貢獻     載具準備、利用與清洗的成本     晶粒厚度必須保持在有限的範圍內 | <ul> <li>必需接觸到接合介面<br/>晶粒的傳輸需注意,特別像是<br/>SRAM與DRAM的多晶粒堆疊</li> <li>晶粒配置期間的微粒管理</li> </ul> |

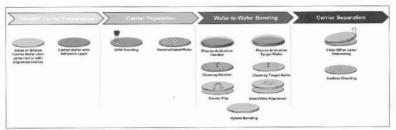

圖1 集體晶粒到晶霞接合方法

(CMOS)影像感測器與各種記憶體與邏輯 技術,也擁有實證的成功經驗。不過,由 於Chiplet不見得都是同一尺寸,晶粒到晶 圆(D2W)的混合接合方式,可能是更加實 際的選項。

對於異質整合,目前有數個不同的 D2W混合接合方法已列入考量,如表1顯 示,每個方法都有其優缺點。哪一種方法 適合用在特定的應用,取決於晶粒尺寸、 晶粒厚度與總堆疊高度等數個因素·以及 如介面設計與密度等的考量。

#### 集體晶粒到晶圓接合

過去幾年內已在矽光子(Silicon Photonics)等應用中實現大量生產的混 合D2W接合方法,是集體晶粒到晶圓 (Co-D2W)接合。在Co-D2W接合中, 晶粒透過截具晶圓轉移到最終的晶圓, 並在單一的流程步驟中完成集體接合。 Co-D2W接合程序的製造流程如圖1顯 示,可分為四大階段,分別是載具準備、 載具布植(Population)、晶圓接合(暫時與 永久)以及載具分離。

在初次晶圓切割程序前,由於接合介面 在晶圓切割膠帶上會朝上置放・因此晶圓 表面會塗上一層保護層,以便在切割與挑 揀過程中維持接合介面的品質。保護層的 材質可能是市售的正光阻劑,以及(或)任 何其它符合使用切割方法的規格,並且隨 後可以用溶劑或透過水溶性清洗過程完全 移除的保護層。透過使用EVG150自動塗 布設備,可以在低拓撲(Topography)的晶 圓保護層上進行旋轉塗布。針對拓撲高於 5微米的晶圓,我們可以使用同樣的設備 進行噴塗。

為了在清洗、晶粒準備與轉移過程中, 使用挑揀D2W黏晶機把晶粒暫時置於集 體晶粒載具上並鎖定位置・載具晶圓會塗 上一層市售的暫時黏著材料。使用的暫時 黏著劑類型,視後加工步驟而定,並且可 以使用EVG850TB暫時黏晶機,讓它接合 在載具品圓上。載具準備過程可以使用不 同的計量系統,例如使用EVG40NT來量 測晶粒配置的精準度,以及使用EVG50 評估來料的晶粒高度的變異、晶粒間的表 面平面性,以及黏著劑的厚度。

塗上保護層切割完成的晶粒則置於集體 晶粒載具上,且接合表面朝上,以方便隨 後可以從晶粒表面移除保護層。我們可以 利用EVG320自動清洗系統,使用溶劑以 及(或)水溶性的清洗化學藥劑,完成這道 移除步驟。

#### 設備與材料

圖2 EVG晶粒到晶圓接合過程系統

在混合接合流程中所使用的集體晶粒載 具與目標晶圓的基體,都會使用電漿活化 結合去離子的水溶性晶圓清洗法進行製 備,接著使用EVG SmartView NT光學對 準器,讓載具晶圓翻面並對準目標晶圓, 再來會使用GEMINI FB自動熔合晶圓接 合系統,讓載具晶圓上的晶粒與目標晶圓 完成接合(圖2)。最後,我們可以使用雷 射或熱解離,讓集體晶粒載具與轉移完成 的晶粒彼此分離。

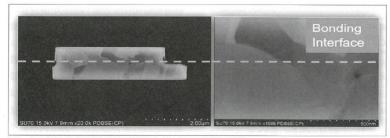

圖3顯示完成混合接合後,轉移完的晶 粒的穿透式電子顯微鏡(TEM)橫切面影 像。在隨後的熱退火過程·銅粒的再結晶 與銅粒生長,會使介面開合再結晶。接合 介面長出的銅粒顯示接合的高品質。利用

次世代的晶粒黏晶機,我們可以期待對準 精度進一步的提升,讓流程的整體晶粒對 準精度遠遠低於1微米。

#### 直接配置晶粒到晶圓接合

針對異質整合應用,還有另一種剛開 始進入實用階段的混合D2W接合方法, 即直接配置晶粒到晶圓(DP-D2W)接合。 這種方法使用挑揀覆晶黏晶機,一次把 一個晶粒轉移到最終的晶圓。圖4顯示 DP-D2W接合過程的製造流程,包含三 個主要階段: 載具布植、晶粒的清洗與活 化,以及直接配置覆晶。

DP-D2W接合流程開始的方式,與 Co-D2W接合流程大致相同,晶粒面

圖3 使用混合接合法的晶粒到晶圓接合介面的TEM模切面影像

圖4 直接配置晶粒到晶圓接合方法

朝上,加到載具晶圓上。DP-D2W與 Co-D2W相比儘管可以提供更高的彈性, 尤其是針對高頻寬記憶體的多晶粒堆疊, 但清洗與活化的挑戰與其它任何熔合接合 技術相同。為了把晶圓從後端研磨與切割 步驟傳送到前端的清洗混合接合步驟,晶 粒常需要在專屬的清洗載具晶圓上重新擴 展,接著載具晶圓進行電漿活化與清洗。 並非直接將載具晶圓與目標晶圓接合,而 是使用挑揀覆晶黏晶機,讓晶粒逐一與目 標晶圓接合。

晶粒清洗步驟是整個流程極為關鍵的一 環,它需要專屬的清洗與活化工具。近期 推出的EVG320D2W,是專為供高度彈性 化的晶粒前處理與活化系統使用所設計, 並以通用的硬體/軟體介面為特色,可以 促成與第三方挑揀系統無縫的整合。依據 產線整合與生產線平衡,它也可以當成獨 立的系統運作。這套系統結合EVG先進的 清洗與電漿活化技術,這項技術在EVG 的W2W熔合與混合接合平台都是現成可

圖5 EVG異質整合技術中心

用的, 並在全球數百個安裝模組上取得驗 證。其特色包括整合的量測模組,可以把 關鍵的流程參數直接回饋給黏晶機,如晶 粒對位精準度與晶粒高度資訊與接合後量 測·以提升流程的管控。

#### 全新異質整合概念的育成中心

製造商為了決定他們個別裝置的最佳接 合方式,必須統合大量的開發專案,這些 專案不但要考量晶圓接合設備本身,還 要考慮涉及的材料,以及相關的設備與流 程。廣泛的流程專業知識不可或缺,而有 辦法取用最新技術也是關鍵。不過,由於 這些系統經常已經在客戶的廠址投入生產 使用,研發或實驗人員可能不太容易接觸

為了因應這些挑戰, EVG成立異質整 合技術中心(HICC,圖5),協助客戶利用 EVG流程的解決方案與專業,促成系統整 合與封裝進展驅動的全新與強化的產品與 應用。HICC成立的初衷是協助客戶將開 發阻礙降至最低,並為EVG提供全新想法 的育成中心。透過HICC, EVG可以協助 加速技術開發、讓風險極小化,並透過異 質整合與先進封裝,開發與市場不同的差 異化技術與產品,同時保證開發還未上市 產品必需的智慧財產最高保護標準。

(本文作者為EVG事業開發總監)

本文英文版已刊登於3DInCites 2021年鑑。